# FLEX 10KデバイスのEABが 提供する利点

TECHNICAL BRIEF 6

1996年8月

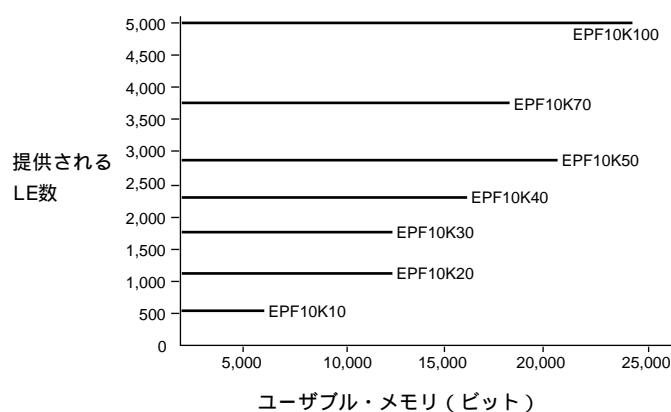

FLEX 10Kデバイスには、エンベデッド・アレイとロジック・アレイが内蔵されています。エンベデッド・アレイは複数のエンベデッド・アレイ・ブロック (EAB) で構成されており、各EABには2,048ビットのRAMを実現することができます。エンベデッド・アレイによるRAMは他のロジック部分に影響を与えることなく構成することができるため、分散型のRAMよりも高いシリコン効率と性能を実現します。FLEX 10Kのアーキテクチャでは、エンベデッド・アレイとロジック・アレイが同時に使用できるようになっています。図1はFLEX 10Kファミリーの各デバイスに提供されているメモリ容量とロジックのサイズを示したものです。

図1 FLEX 10Kデバイスのロジック・エレメント (LE) 数とメモリ容量

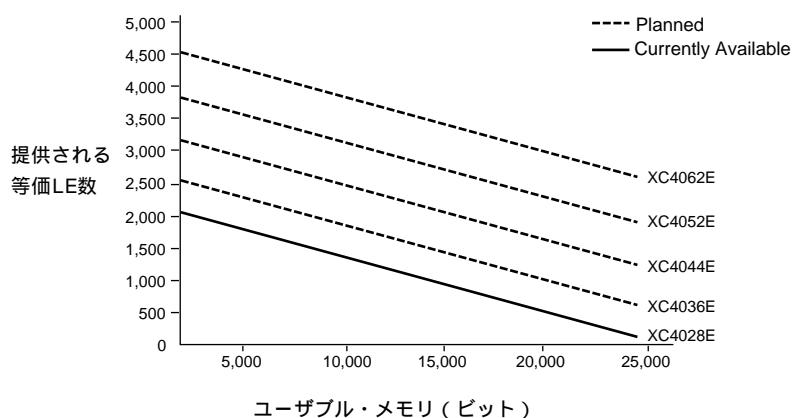

分散型のRAM構造となっているFPGAにはエンベデッド・アレイが内蔵されていません。通常、これらのFPGAには、ロジックまたは小規模なメモリ ( $32 \times 1$  または  $16 \times 2$ ) のいずれかにコンフィギュレーションすることができるコンフィギュラブル・ロジック・ブロック (CLB) が内蔵されています。分散型のRAMは小規模なオン・チップRAMを実現する場合に便利ですが、複雑なデザインではさらに大規模なRAMブロックが必要となります。分散型のRAMでは、このような場合にロジックとメモリのサイズのトレード・オフを考慮する必要があります。図2は、メモリとロジックとの間に存在するトレード・オフの関係を示したものです。

図2 Xilinx XC4000EXにおけるロジックとオン・チップRAMのトレード・オフ

Source: Xilinx XC4000 Series FPGA Product Specification v1.00

## 性能

分散型のRAMを使用しているFPGAでは、性能が実現されるメモリのサイズとメモリを構成するために使用される配線リソースの量に依存します。大規模なオン・チップRAMをFPGAに構成するためには、小規模なRAMのブロックを多数使用して相互に配線する必要があるため、その性能が低下してしまいます。これに対して、エンベデッド・アレイによって実現されるRAMは、こうしたことにより影響されることはありません。各EABには、一定したしかも最適化された性能を得るために必要なアドレスのデコーディングと同期化の回路がすべて含まれています。表1はFLEX 10KファミリとXilinxのXC4000Eファミリの性能を比較したものです。

表1 オン・チップRAMの性能比較

| デザイン                          | Xilinx<br>XC4000E<br>-3スピード・グレード <sup>1</sup> | Xilinx<br>XC4000E<br>-2スピード・グレード <sup>1</sup> | Altera<br>FLEX 10K<br>-4スピード・グレード <sup>2</sup> | Altera<br>FLEX 10K<br>-3スピード・グレード <sup>2</sup> |

|-------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------|------------------------------------------------|

| 入出力がレジスタ付きの256×8<br>オン・チップRAM | 63MHz                                         | 80MHz                                         | 86MHz                                          | 105MHz                                         |

<sup>1</sup> Source: Xilinx XC4000 Series FPGA Product Specification v1.00

<sup>2</sup> Source: Altera 1996 Data Book

## 使用効率

FLEX 10KのEABのアーキテクチャでは、提供されているRAMのすべてのビットを使用するようになっており、同時にロジックの構成には提供されているすべてのLEを使用することができます。これに対して、分散型RAMを使用しているFPGAに大規模なメモリを構成する場合は、小規模なRAMブロックの出力をマルチプレックスし、RAMへの書き込みをコントロールするためのロジック(CLB)が必要になります。さらに、これらのロジックの構成に使用されるCLBはRAMとして使用することができなくなるため、分散型RAMのデバイスではオン・チップRAMの容量が増加すると共に、使用可能なロジックのサイズが大幅に減少します。FPGAによっては、表示されているオン・チップRAMの最大容量を実現する場合に、すべてのCLBをRAMとしてコンフィギュレーションしなければならないこともあります。この分散型RAMを使用しているFPGAでは、大規模なRAMブロックの実現に小さなRAMを相互に接続するためにロジックも必要になることから、表示されている構成可能な最大RAM容量は誤解されやすいものになっています。

## 全体のチップ・サイズ

同期型のRAMは非同期型のRAMよりも一般的に使いやすくなっていますが、同期化のための回路が必要になります。FLEX 10KのアーキテクチャにはEABあたりで1つの同期化回路のみが必要です。例えば、100,000ゲートのEPF10K100は12個のEABを持っており、同期化のために必要な回路数が12だけになります。(表2を参照)

表2 FLEX 10Kファミリに要求される同期化回路

|                             | EPF10K10 | EPF10K20 | EPF10K30 | EPF10K40 | EPF10K50 | EPF10K70 | EPF10K100 |

|-----------------------------|----------|----------|----------|----------|----------|----------|-----------|

| 同期化のため<br>の回路数 <sup>1</sup> | 3        | 6        | 6        | 8        | 10       | 9        | 12        |

<sup>1</sup> Source: Altera 1996 Data Book

分散型RAMのアーキテクチャはFLEX 10Kに比較して、同期化のための回路がさらに多く必要になります。例えば、分散型のRAMを使用しているXilinxのXC4000EXでは、各CLBが独立したメモリ・ブロックとなっており、同期型のRAMの実現にはCLBあたり2つの同期回路が必要です。例えば、62,000ゲートのXC4062EXは2,304個のCLBを持っていますが、これをすべて同期型のRAMに構成する場合には、4,608個の同期回路が必要になります。(表3)このため、CLBをロジックとして使用したい場合でも、オン・チップRAMの同期化のための回路に全体のリソースの多くが使用され、大きな制限を受けることになります。これによって、ダイ・サイズとコストが上昇する結果になります。

表3 XC4000EXファミリに要求される同期化回路

|                         | XC4028EX | XC4036EX | XC4044EX | XC4052EX | XC4062EX |

|-------------------------|----------|----------|----------|----------|----------|

| 同期化のための回路数 <sup>1</sup> | 2,048    | 2,592    | 3,200    | 3,872    | 4,608    |

<sup>1</sup> Source: Xilinx XC4000 Series FPGA Product Specification v1.00

---

下記のドキュメントには、さらに詳しい情報が提供されています。カッコ内の番号はアルテラのドキュメント・ナンバです。

データシートおよびデータシート補充版

プロダクト・インフォメーション・プリティン

- FLEX 10K Embedded Programmable Logic Device Family Data Sheet (A-DS-F10K-02) ---日本語版有り

- PIB20 ( Benefits of Embedded RAM in FLEX 10K Devices ) ( A-PIB-020-01 ) --- 日本語版有り

- FLEX 10K Embedded Programmable Device Family Data Sheet Supplement ( データシート補充版 ) ( A-DSS-F10K-2.2 ) ---日本語版有り

---

## 日本アルテラ株式会社

〒163-04 東京都新宿区西新宿2-1-1

新宿三井ビル私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487

### 本社 Altera Corporation

2610 Orchard Parkway,

San Jose, CA 95134-2020

Telephone : (408) 894-7000

Fax : (408) 944-0952